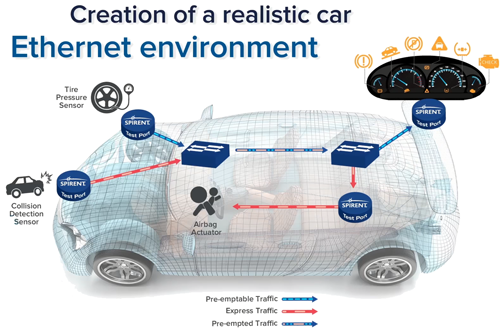

Ethernet is being used to move the world’s data, from planes, trains and automobiles to industrial motor control, autonomous vehicles and the Internet of Things (IOT). The demand to create systems of systems has never been greater, and brings in new challenges to development engineers. They need to gain knowledge on new technologies and on techniques for testing in order to design high speed networks for safety-critical signals. Designing a quality product on time and under budget can be difficult if not impossible without the proper expertise. The key to succeed in this challenge is to uncover product defects in early design stages. But how can this be done without all of the other members in the network? The answer is testing using AUTOSAR, OPEN Alliance or Avnu test suites to ensure conformance to industry standards.

TSN specifications are defining ways to enable zero congestion loss of time-critical data flows. But loss due to congestion is only half of the issue, as network designers and architects also must measure worst-case end-to-end latency within the network. Latency measurements must also consider primary and redundant flows during fault recovery conditions. This is to be able to measure normal vs redundant data path flows in a live network because it is extremely critical to industrial motor control applications. Using the Spirent emulated devices, you can quickly check the Best Clock Master Algorithm (BCMA) inside real devices on the network to ensure they recover from faulted conditions.

Testing the network with a mix of real devices and Spirent’s Emulated Devices with gPTP functionality will enable designers to find out what scenarios help them to optimize and check network traffic to ensure no loss of time-critical data flows. This is achieved using Spirent embedded counters and timers:

Over 40 measurements tracked in real-time for each received stream including:

Advanced sequencing: In-order, lost, reordered, late and duplicate

Latency: Avg, min, max and short-term avg; first/last frame arrival timestamp

Latency modes: LILO, LIFO and FIFO

Data integrity: Generate Errors: IP checksum, TCP/UDP checksum, frame CRC, embedded CRC and PRBS bit errors

Histograms: Jitter, Inter-arrival, Latency, Sequence

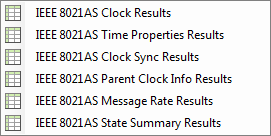

Automated Summary of Timing and Synchronization for IEEE 802.1 – gPTP

Spirent also automatically calculates the following IEEE802.1as gPTP Clock information:

IEEE802.1as Clock Results

States: Clock Identity, State, Clock Accuracy

Timers: Current, Min, Max, Avg Mean Path Delay

Counters: TX / RX Announce, TX/RX Sync, TX / RX Follow up, TX / RX Peer Delay Request, TX / RX Peer Delay Response, TX / RX Peer Delay Follow up

IEEE802.1as Time Properties Results

States: gPTP Time Scale, Current UTC offset Valid, Leap59, Leap61, Time/Frequency Traceable, Time Source

Counters: Current UTC offset

IEEE802.1as Clock Sync Results

Timers: Time of Day

Counters: Current offset, Positive / Negative offset Peak and deviation, Current, Min, Max, Average Mean Path Delay, Average offset plus / minus deviation, Step Removed, Minimum Pdelay Request Interval, Peer Mean Path Delay, Sync / Follow-up / Pdelay Correction Field Response and follow-up, Invalid Timestamp count

IEEE802.1as Parent Clock Info Results

States: Parent Stats, Step Mode

Timers: Observed Parent offset scaled log Variance, Observed Parent Clock Phase Change Rate, Grandmaster Identity, Grandmaster Clock Class, accuracy, offset Variance, Grandmaster Priority 1, 2

IEEE802.1as Message Rate Results

Counters: Announce Rate: Tx / Rx Min, Max Average Packets per second,Sync Rate: RX Min, Max, Average Packets per second, Follow up Rate: RX Min, Max, Average Packets per second, Peer Delay Request Rate: RX Min, Max, Average, Peer Delay Response Rate: RX Min, Max, Average, Peer Delay Response Follow up Rate: RX Min, Max, Average

IEEE802.1 State Summary Results

Counters: Faulty, Disabled Count, Listening Count, Pre-Master Count, Master / Slave Count, Passive, Uncalibrated Count, 802.1as up / down

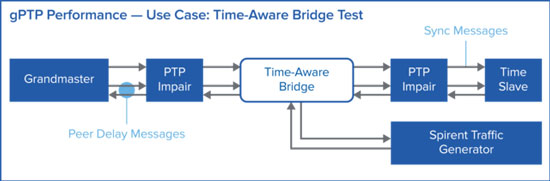

Impairment / Error injection - Timing and Synchronization for IEEE 802.1 – gPTP

As you are deploying a time-aware network we must take into consideration timing errors. The two main contributors to timing errors are the accuracy of the correction field and the peer delay calculations for each member in the network. Do they reflect the actual delay experienced by the sync messages? Possible errors:

Variable Errors

Quantization errors in time stamps

Synchronization/rounding errors in local DUT clocks

Phase noise in oscillators

Fixed Errors

Asymmetric delays in physical layer ie: time stamp type and point

Cable lengths between forward and reverse paths

In a typical device under test the application functionality turnaround time can and will impact the downstream path delay calculation when internal DUT hardware and software resources are shared between the application functions and network communications.

Spirent provides a test bed that emulates, measure and impair gPTP networked devices using industry proven techniques and products to help develop robust products with accurate timing.

Want a step by step guide to conducting the right tests?

Get the full Time-Sensitive Networking Automotive Playbook

Or learn more about our automotive testing solutions here: